【计算机系统】CPU指令执行流程与指令流水线原理

【计算机系统】CPU指令执行流程与指令流水线原理

一、指令执行流程 冯诺依曼架构CPU指令执行的五个阶段:

| 阶段 | 涉及的功能部件 |

|---|---|

| IF | 指令寄存器IR、程序计数器PC |

| ID | 指令译码器ID |

| EXE | CPU内各个单元:ALU、Cache、Registers .etc |

| MEM | |

| WB | 状态寄存器FR、Registers. etc |

1、取指阶段(IF, Instruction Fetch) 在上一个指令周期时,程序计数器PC中记录的是下一条指令的内存地址。因此IF阶段CPU指令寄存器按照PC的地址从主存中取得一条指令,当前指令被取出后,PC更新到下一条指令的地址。

2、指令译码阶段(ID, Instruction Decode) 在ID阶段,指令译码器按照预定的指令格式,对取回的指令进行拆分和解释,识别区分出不同的指令类别以及各种获取操作数的方法。

3、执行指令阶段(EXE, Execute) 通过对指令的译码,CPU已经知晓这条指令要如何执行,因此EXE阶段就是通过操作控制器OC,按确定的时序向相应的部件发出微操作控制信号以对指令要求的特定操作进行具体实现。EXE阶段CPU的不同部分(如ALU、寄存器组等)被联合起来,以实现指令所需的操作。

4、访存取数阶段(MEM, Memory) 根据指令需要可能要访问内存,读取操作数。MEM阶段根据指令地址码(如果有要求的话)得到操作数在主存中的地址,并从主存中读取该操作数用于运算。

5、写回阶段(WB, Write Back) WB阶段把执行指令阶段的运行结果数据“写回”到某种存储形式:

①写入CPU的内部寄存器中,以便被后续的指令快速地存取

②写入内存

③改变FR中标志位状态(如果需要改变的话),用来影响接下来程序的动作

WB阶段结束后,若无意外事件(如结果溢出等)或异常中断发生,计算机就接着从程序计数器PC中取得下一条指令地址,开始新一轮的循环。上述五个阶段在具体实现过程中会引入指令流水线来提高效率。

二、指令流水线(Instruction Pipeline) 指令流水线概念的提出是为了提高CPU处理指令的效率。

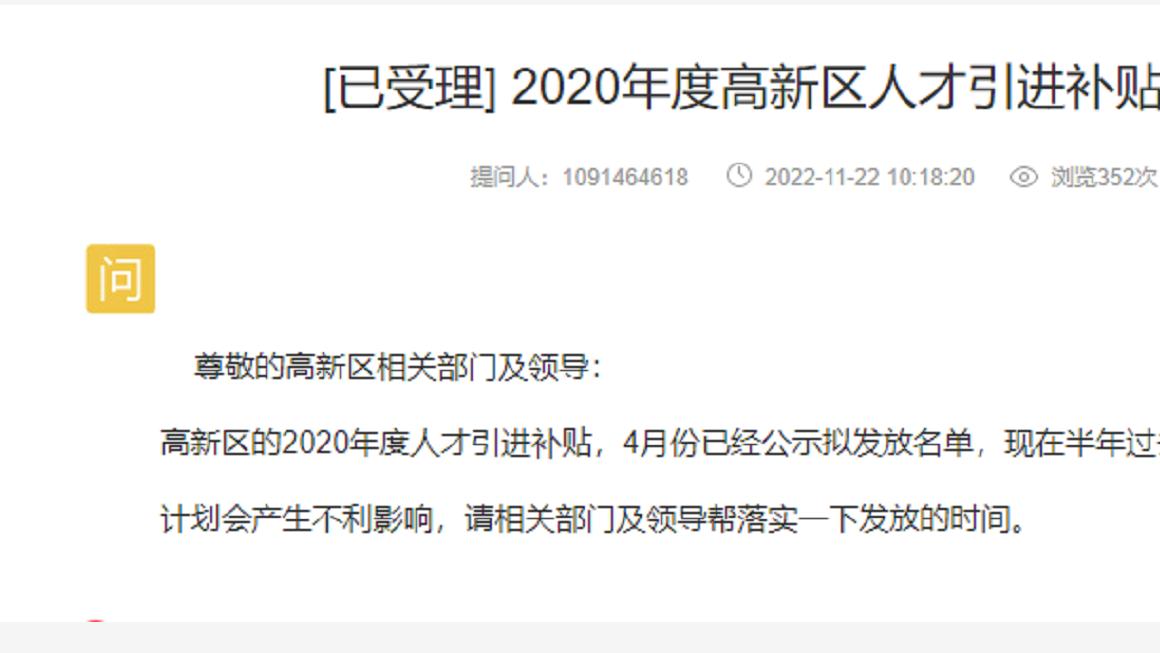

假设将CPU执行一条指令按照流程分为四个步骤如图1(ii)

文章图片

文章图片

图1 考虑一个完全不采用流水线的系统如图3(i),对于一组指令序列,CPU总是等某条指令的全部过程都执行完之后再开始下一条指令。与之对比的是图1(ii)的指令流水线,在第一条指令完成IF后,第二条指令就可以开始IF,依次类推。直观地,指令流水可以大幅提高CPU处理指令的效率。

1、指令流水线基本概念 ①指令流水周期:将一条指令划分为不同的步骤涉及到的一个重要问题就是——不一致的划分现象,即每个步骤完成的时间不均匀,例如在经典划分中,IF,WB的速度比较快而EXE速度较慢,如图2所示阴影部分为指令步骤所需的时间。因此必须把流水周期设置为单级操作的最大时延。指令阶段间的指令转移(例如IF→ID)是由时钟信号控制的,驱动这条指令流水工作的时钟周期应该要等于这个最大时延。

文章图片

图2 ②CPI(Cycles Per Instruction):即每条指令经过整个流水线所需周期数,它与各指令有关,不同的指令,CPI也不相同。因此,一般使用平均CPI表示

③ILP(Instruction Level Parallelism):即指令级并行度,是指当指令流水线被充分利用时,一个基本周期内并行执行的指令数

④指令发射速率:指在每个周期内发射的指令数,在数值上等于超标量处理机的级数。

2、影响流水线性能的因素 【【计算机系统】CPU指令执行流程与指令流水线原理】①数据相关:如第一条指令的输出为第二条指令的输入,则第二条指令必须等待第一条指令执行完毕而不能直接进入流水,造成流水线效率下降

②控制相关:如遇到分支判断指令,那么该指令可能顺序执行,也可能分支跳转到其他位置,造成流水线断流。

引入流水线会提高CPU指令处理效率,但过深的流水等级会使数据相关和控制相关的副作用增大,反而又降低了CPU工作性能。

3、流水线的改进技术——超标量技术

文章图片

图3 采用资源重复的并行性思想,设置多条指令流水线和多个功能部件。每个周期发送多条指令(即指令发射速率大于1),同时并行地对多条指令进行流水处理

推荐阅读

- 宽容谁

- 我要做大厨

- 增长黑客的海盗法则

- 画画吗()

- 2019-02-13——今天谈梦想()

- 远去的风筝

- 三十年后的广场舞大爷

- 叙述作文

- 20190302|20190302 复盘翻盘

- 学无止境,人生还很长